Actually, we knew that there had to be multiple chips inside the S1, because we did a pseudo-teardown last year, based on Apple’s promo video at the time. It turns out that the S1 is actually an assembly of chips on a dedicated printed circuit board (PCB) substrate, with over 30 chips plus many passive components. So it is more accurately described as a System-in Package (SiP).

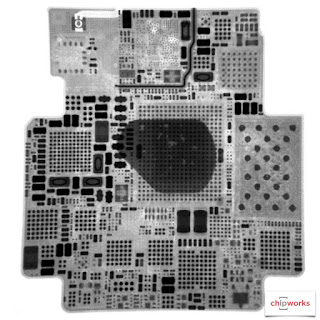

This was confirmed when we took the S1 out of the case and x-rayed it;

And we identified many of them;

Actually, we did two cross-sections along the lines shown here;

This is section P1AS2;

On the left is the Dialog PMU; in the centre is the Apple APU (APL0778), with an Elpida DRAM co-packaged; and at the right is the Sandisk 64-Gb flash, including the controller chip and a spacer die. There seemed to be a wide-spread assumption that the APL0778 would be in a Package-on-Package (PoP) stack with the memory, as in the iPhones, but here it is in a straight-forward two-die stacked package.

If we look closer, we can see that the S1 uses conventional assembly techniques, but once all the components are on the 4-layer PCB, the whole thing has been over-molded with more molding compound, and then plated with metal to give the stainless-steel looking finish. A close-up of the right edge shows what I mean;

There are two 32-Gb flash dies in a conventional package with its own substrate, which is flip-bonded onto the PCB, covered with the SiP over-molding, and the exterior is metallized, giving the silver finish.

Section P1AS1 has the Broadcom BCM4334 in the centre, and the AMS NFC booster chip on the right. At left is a co-axial RF test socket.

Again, if we look closely, we can see that underfill has been used across the whole PCB before the over-molding was performed. Another feature of note is the I-shaped EMI shielding on the right of the BCM die, molded into the SiP – this is the first time we have seen this in any sort of package. In the x-ray image above, it surrounds the BCM chip, separating it from the other components. Here we are in close-up;

In effect the complete S1 assembly has EMI shielding since (with the exception of the accelerometer/gyro) the whole thing has a metal coat, mostly copper with a skin of iron/chromium. Such a coating will also inhibit moisture ingress, a good thing since I’ve heard tales of folks showering while wearing a Watch, and wrists can get a bit sweaty anyway.

A big question for us is – who supplied such an innovative package? Press commentary has identified the provider as ASE (Advanced Semiconductor Engineering Inc.) of Taiwan; and I presented at an IMAPS wearables workshop back in June, and when I got to the Watch analysis the attendees from ASE shared a few knowing looks.

The last quarterly analyst call from ASE also included this graphic, which details quite nicely the SiP concept, and includes details such as the EMI shielding:

ASE has also had more revenue from SiP this quarter, “In terms of overall, the SiP revenue accounted for about 22% in the second quarter, up from 15 a quarter ago because of the EMS SiP product ramp up.” Interestingly, they are also running below break-even on the SiP product (In response to a question as to whether all SiP projects are losing money, or just the one; “Thank God it is. It's only this particular project that is running below break-even. Other things are moving very nicely.”).

Given these comments, I’m inclined to believe the press on this one – ASE is the supplier.

Another nugget comes from perusing the transcript of the call – “What kind of application and what kind of customers you are working with for the new SiP projects?

Tien Wu replied, “I don't think I'd comment specifically but I’m pretty sure you will find some new products that have come out pretty soon. Sorry.”

He also noted, “We promise each other will never come out specific customers. So I will give you a non-qualifying, non-specific answer. We are expanding the SiP coverage to the cellphone, to the tablet in that particular arena. Hopefully, we can report more revenue, more penetration.”

I take that to mean that we may well see this style of SiP in the new iPhone and iPad later this year – more fun!

.png)

.png)

.png)